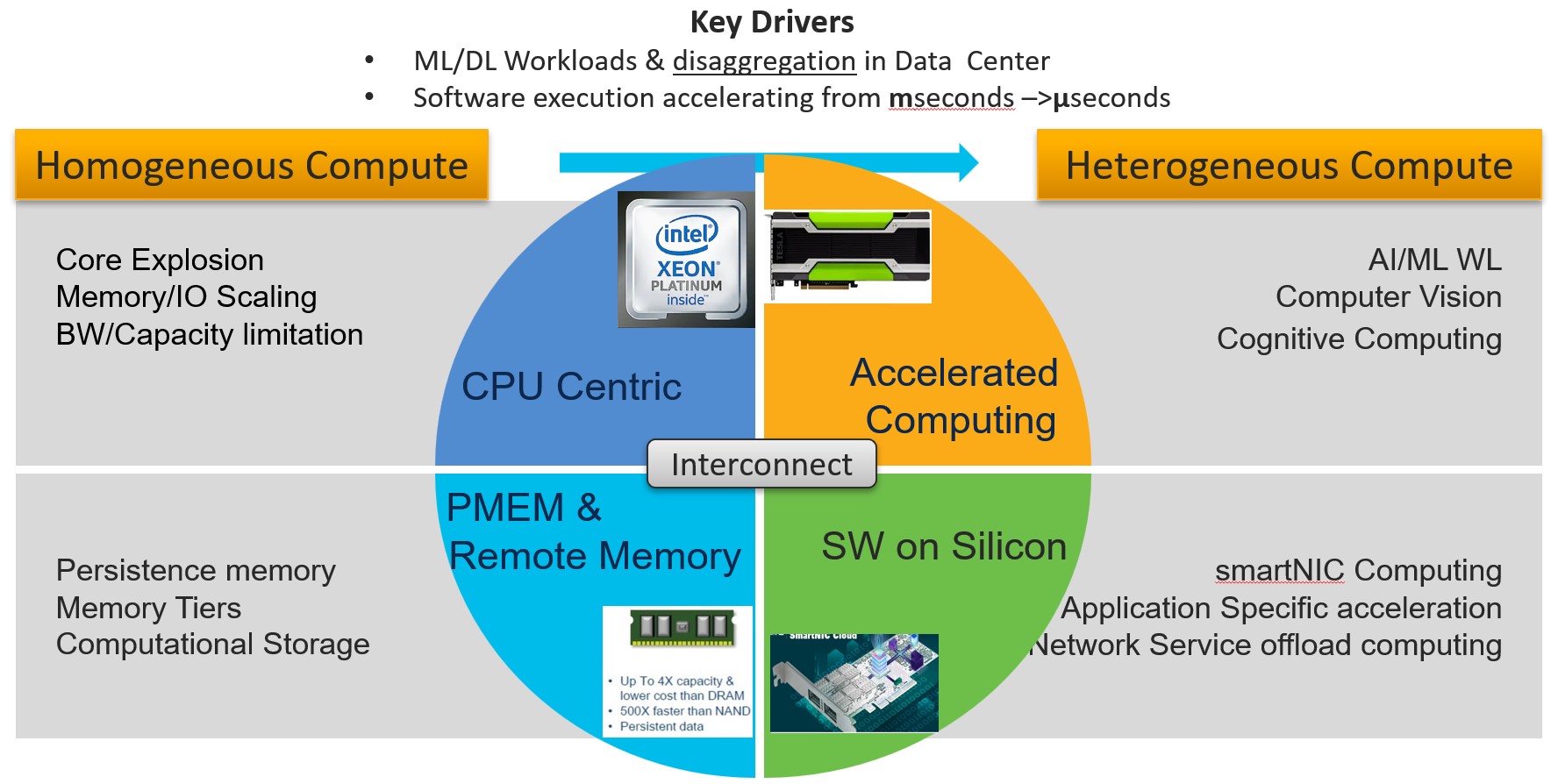

正像概述 在我的上头博客范式转向多式计算关键驱动程序正在AI/ML领域出现新工作量,需要最优增产硬件和软件框架系统架构趋势和需求驱动异质计算需求的同时,值得指出的是软件方面类似趋势正在发生X86/ARM/MIPS/RISCV代码库、嵌入内核库、深学习框架工作如Caffe、TensorFlow、PyTorrch支配软件平台优化执行时间

异式计算带来了资源可编译性挑战 IO连接所有资源这些资源从加速计算农场GPUs、SNIC计算子系统和数据边缘或附近存储-AKA计算存储

GPU等加速计算起始级成本非常昂贵。 从TCO角度讲,拥有可虚拟化、构件和按需共享资源至关重要。 本质上新服务器架构必须是动态和弹性型的,没有控件资源并有能力全时转换使用资源计算

旁对端数据运动资源间通信绕过中央CPU消除冗余数据复制需求帮助减少IO系统总线流量并提升延时性

IO布料将多子系统绑在一起?单IO布料法可能无法满足离数据中心的不同需求多构型架构方法至关紧要

下一代互连需求

以太网从协议认知IO/Storage流量透视接收服务器数据延时和一致性问题使它在负载/存储IO最低层选择不妥,通常发生于nS的10s

完全实现混合计算新IO布料的潜力

- 负载/轮胎语义减轻对软件栈间接传输数据的需求

- 低延时高带宽-32/64/128Gbps

- 同比通信和一致性

- 无缝断存分层资源-内存和/或@子系统级

- 网络-NIC故障

- 真实织物级指令结构分解

PCIeIO技术提前填充延时段需求,但从速度和特征角度演化缓慢,核心爆炸引出IO带宽问题数项专有开源努力创建新IO互连但他们都找不到比例推力,直到CXL(计算Express链接)互连高带宽Lo延缓度至关紧要,但正是协议底层栈需要大修OS应用利用CXL基础无处不在PCIe物理分层并添加高效协议栈

内存带宽

内存带宽提高核心计数挑战 可能对IO互连作用最大

处理器核心数翻四番 从32倍到128倍 并在未来几年内存通道和带宽无法缩放@1.5-2x引起带宽/核心不匹配。核心计数超过128时,内存通道速度增量变化将不足以维护带宽/核心比令问题更糟的是,标准机架因子中12道以上每个套接字克服所有这些限制需要从 CPU解码内存内存脱钩需要量级更多互连带宽度多带宽制作内存多租量需要不同于电气域的IO传输网络将发展成网络资源并使用 sNIC/DPU计算,

UCX X-Series架构综合新思想、趋势并用联动方式下注以利多式计算解决现有需求并允许客户按需采行并扩展混合云模型同时平衡总公司

并讨论内存分类需要非电化IO传输

资源类

UCS X-Series-Cecomblog串行未来-3之2

连接CISCO